铠侠株式会社(Kioxia Corporation)日前宣布开发出创新的储存单元结构“Twin BiCS FLASH”。该结构将传统3D闪存中圆形存储单元的栅电极分割为半圆形来缩小单元尺寸以实现高集成化。新的单元的设计中采用浮栅电荷存储层(Floating Gate)代替电荷陷阱型电荷存储层(Charge Trap),尺寸也比传统的圆形单元更小。

铠侠已率先在此单元设计中实现了高写入斜率和宽写入/擦除窗口。同时,铠侠也证明这种新的单元结构可应用于进一步提高容量的超多值存储单元中。铠侠于12月11日(当地时间)在美国旧金山举行的IEEE国际电子器件会议(IEDM)上发表了上述成果。

截止到目前,诸如BiCS FLASH之类的3D闪存通过增加单元的堆栈层数以实现大容量。但是,因为单元的堆栈层数超过100层,高纵宽比的加工越来越困难。为了解决这一问题,铠侠在新的单元结构中将常规圆形单元的栅电极分割为半圆形以减小单元尺寸,并且可以通过较少的单元堆叠层数实现更高的位密度。

得益于曲率效应,与平面单元相比,圆形存储单元可以确保写入窗口并有效抑制写入饱和。新的单元结构中采用了半圆形,可以继续利用曲率效应。另外,新的单元在电荷存储层中采用了高电荷捕获率的导体材料,并且在阻断膜(BLK Film)中采用了高介电常数的绝缘材料以减少漏电流(图1)。

图1.Fabricated semicircular FG cells (a) Cross-sectional view (b) Plane view

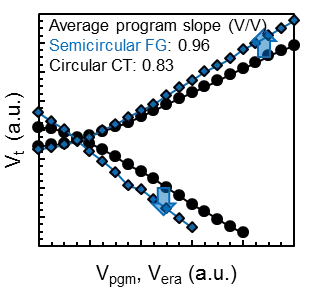

实验表明,与圆形存储单元相比,半圆形结构具有更小的单元尺寸,更高的写入斜率和更宽的写入/擦除窗口(图2)。

图2.Experimental program/erase characteristics comparing the semicircular FG cells with the circular CT cells

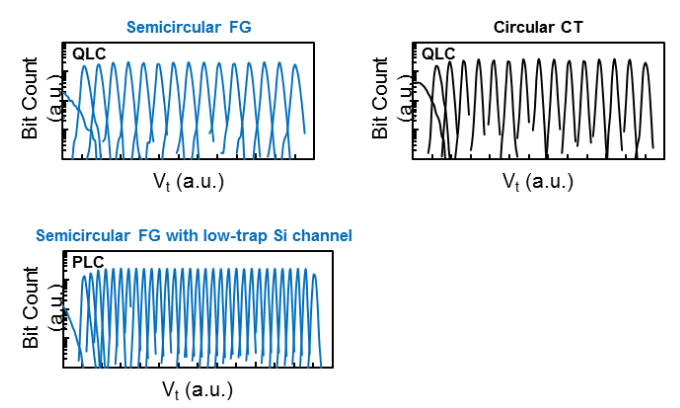

另外,仿真显示,得益于特性的改善,尺寸更小的半圆形存储单元预期可以取得与传统圆形单元中4位/单元(Quadruple-Level Cell)相等同的Vt分布。同时,通过采用低陷阱硅通道,更可实现5位/单元(Penta-Level Cell)的Vt分布(图3)。

图3.Simulated Vt distributions after programming using calibrated parameters

上述结果显示,半圆形存储单元是实现大容量超多值单元的可行方案。

今后铠侠将继续为该技术的实用化进行研发。另外,铠侠正在积极推进闪存技术的研发,在此次IEDM 2019,铠侠还发表了其他6篇论文。

来源:铠侠株式会社,截止到2019年12月12日。