将来十年,存储市场仍将继续追求存储的密度、速度和需求的平衡点。虽然各个厂家的技术侧重点不尽相同,但铠侠(原东芝存储器)对 3D XPoint 之类的堆叠类存储方案的前景并不看好。在今年的国际电子设备会议(IEDM)上,该公司宣布了 BiCS 闪存系列和即将推出的 XL-Flash 技术,并且附上了一份展现将来愿景的幻灯片。

动态随机存储器(DRAM)、闪存(Flash)和“存储级内存”(SCM),是当前市面上的三大发展方向,铠侠也对英特尔和美光的 3D XPoint 长期愿景进行了展望。

过去几十年,闪存的浮栅和电荷陷阱技术,已经历多次变化。新开发的存储器,其状态取决于单元中介质的电阻或自旋,而不是电压。

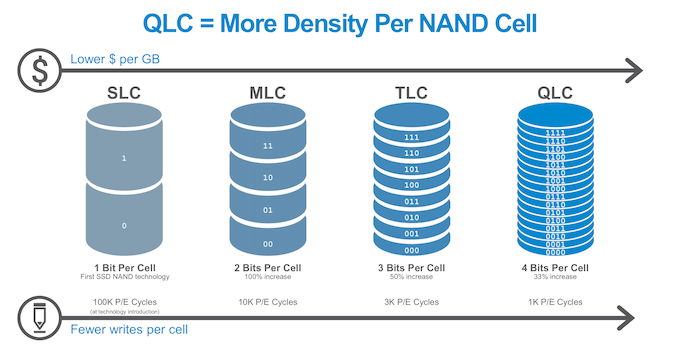

传统上很容易将每个单元视作不同值的“0”或“1”。但因为材料类型的发展,每个单元已能够容纳更多的状态(SLC、MLC、TLC、QLC 等)。

此举能够轻松获得倍增的容量,但也对检测电路的精准度提出了更高的要求,通常可增加单元大小、或降低总体密度来实现。

铠侠当前的 BiCS 闪存技术,依赖于在塔中堆叠多层浮栅单元,然后在 xy 方向重复该设计以增加容量。目前,该公司已大量推出 TLC 和 QLC 产品,并希望打造面向特殊应用的每单元 5 比特位产品。

BiCs 系列产品的设计层数也在不断增加,从 32 层增加到 48 层,再到 64 层和 96 层,预计将来会增加 128 层以上。与其它方法相比,层数的添加,还是相对更加容易的。

另外,铠侠还在开发一种名叫 XL-Flash 的新型闪存。传统闪存以“页面”和“块”的方式工作,而存储类内存以“比特位”的方式工作。

这意味着,虽然 DRAM 可访问每个比特位并对其进行修改,但在闪存中,这意味着任何写操作都需要一次写入整个页面,写入的损耗也成倍更大。

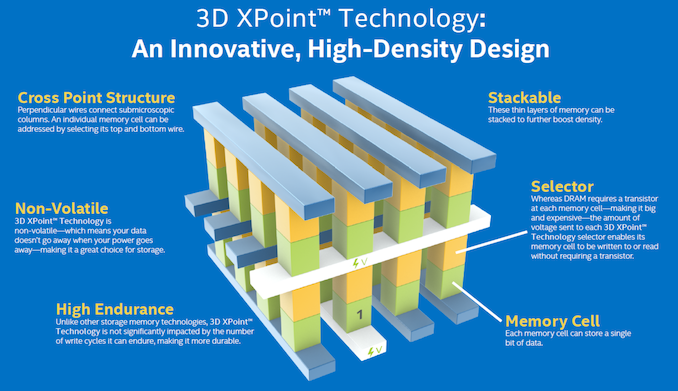

3D 堆叠式存储单元的工作方式与闪存有所不同,以 3D XPoint 为例,其使用相变材料来改变存储单元的电阻,并可以通过电子选择器开关进行访问。

通过交替改变字线和位线的方向来构建存储器,以保留 SCM 的比特位可寻址特性。如需堆叠更多的层数,也只需添加额外的字线和位线,以及其间的单元。

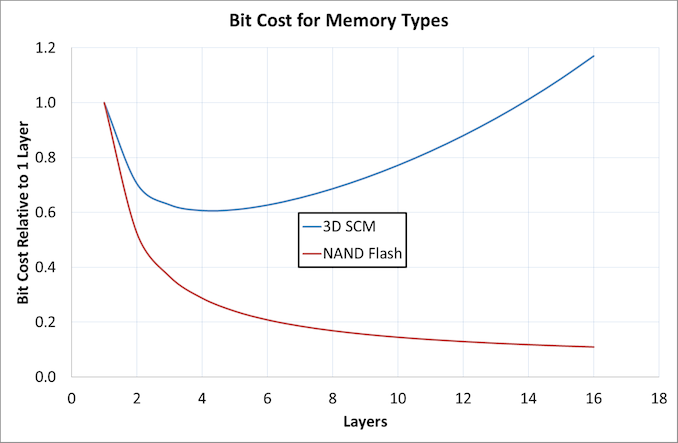

即便如此,铠侠仍不看好 3D XPoint 的前景。首先是相对于层数的每比特位成本,层数的增加会带来更高的复杂性,控制电路会损失一部分面积,产能损失的影响也更大。

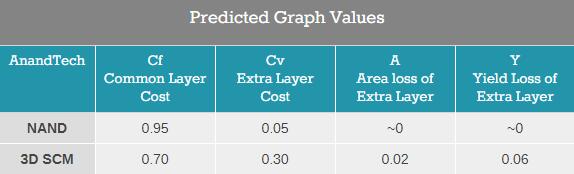

相比之下,3D NAND 技术要成熟得多,市面上已大量上市 90 多层的产品,且无人否认层数堆叠是一种行之有效的方法,因其面积上的损失几乎为零、产量的损失也极低。

在制造过程中,3D NAND 的某些蚀刻和填充步骤,可一次覆盖很多层。相比之下,3D 堆叠 SCM 技术,仍未充分扩展到单层设备之外的市场。

铠侠数据显示,虽然其 BiCS 闪存在经过 10 层时会降低到每比特成本的渐近值,但与单层方案相比,3D 堆栈 SCM 最多只能将 4-5 的成本降低到每比特成本的 60%(之后就开始飙升)。

原因是后者未能受益于数十年改进的复杂工艺,导致每层的成本增加、面积的损失、以及产量的下跌。为构建 3D 堆栈存储器,这是一个艰苦的过程。每多一步骤,良率也就更低。

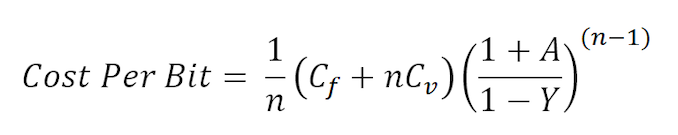

如上方公式所示:其中 n 为层数,Cf 为公共层的成本,Cv 是每增加一层的成本,A 是添加一层造成的面积损失,Y 是单层的产量损失。

有鉴于此,铠侠在会议上称,在 3D SCM 的情况下,12 层左右的每比特位成本还是相当的。但若层数增加到 NAND 闪存一样多(以 64 层 SCM 为例),单层每比特位成本就暴增到 50 倍了。

即便强力推动对 3D 堆叠式 SCM 的支持,当今 4 层以上的堆叠预测成本也已经过高,且未考虑到潜在发展的这项技术在将来的变数。

综上所述,SCM 确实可在内存领域提供超大的数据池,每 GB 成本较 DRAM 低很多。但长期看来,在将来很长一段时间内,闪存仍将在行业内占主导地位。